【多PPT打包】SV硬件设计及建模.rar

”SV 硬件设计 建模“ 的搜索结果

为了保持仿真与综合一致,SV提供了unique和priority的声明,结合case,caseX和casez来进一步实现case对应的硬件电路。@*的敏感列表可能表达不完全,例如一个过程块调用一个函数,那么@*则只会将该函数的形式参数自动...

它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力

Verilog时序逻辑硬件建模设计(一)锁存器D-latch和触发器Flip-Flop没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出...

Verilog/System Verilog 语法说明

SV、UVM与验证思想

标签: 芯片

和C相似:typedef下图中:枚举类型RGB的初始值是redverilog中替代enum的方法:参数化SV中的改动:用enum代替了之前的define,这里的enum为缺省类型下面我们用enum {wr , ld , stro} 例化了两种变量如果大括号里面...

接口interface

通过这种方法,激励可以被应用到设计和参考模型中,在某个抽象层次,通过被测设计和参考模型的输出被校对,黑盒验证存在下列主要的缺点:很难验证和设计相关的特点、很难调试、要求一个精确的参考模型。sv基本语法:...

48.接口与模块不同的是,接口不允许包含设计层次,即接口无法例化module,但是接口可以例化接口。65.接口经常会有关信号集成在一起,这意味着对于拥有多组不相关的设计而言,它可能需要多个接口实例才能完成与其他...

4、数字集成电路的设计流程。5、数字设计流程中每个阶段主要做哪些工作?最主要的EDA工具有哪些? 1、常见的EDA仿真工具有哪些?Debug工具有哪些? 常见的仿真工具如下: Mentor(明导)—>Questas...

SV绿皮书提炼笔记(五)

标签: fpga开发

.sv文件是实现硬件设计的关键文件,它提供了一种有效的方式来编写和管理Verilog代码。 ### 回答2: Verilog .sv文件是指Verilog硬件描述语言(HDL)的源代码文件,其中包含了用于描述数字电路行为和结构的语句和...

SV环境构建(第一部分),包括数据类型,模块定义与例化,参数、宏定义的使用,接口

本文主要摘自《systemVerilog硬件设计与建模》

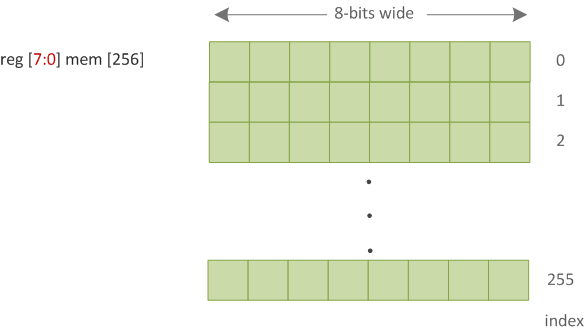

SV总结(文字版) 目录 第一章 验证导论 3 1.1. 测试平台 3 1.2. 为什么要用sv,相比于Verilog有什么优点 4 第二章 数据类型(重点) 5 2.1. 数据类型 5 2.2. 二值逻辑和四值逻辑有哪些 6 2.3. 数组类型的特点和...

SV中$unit编译单元

推荐文章

- C++ map的常用用法(超详细)(*^ー^)人(^ー^*)_c++ map用法-程序员宅基地

- EmEditor 主题 Minimal_emeditor主题-程序员宅基地

- C++学习笔记——C++中四个点代表什么意思?_c++四个点什么意思-程序员宅基地

- Cython的简单使用-程序员宅基地

- ES6新特总结_new easy let 选择那个不同的-程序员宅基地

- idea 如何配置软回车_idea 软换行什么意思-程序员宅基地

- Vue 2项目如何升级到Vue 3?_vue2项目换成vue3-程序员宅基地

- Activiti工作流使用详细介绍_activiti开启工作流-程序员宅基地

- 十大排序算法总结(c++版本)-程序员宅基地

- 新颖的基于BS结构的毕业设计题目50例_bs实训题目-程序员宅基地